Analizator stanów logicznych

Tym razem o dwóch rzeczach na raz, ale w sumie o jednej:-) Czyli nowa moja zabawka: analizator stanów logicznych oraz zajawka diversity do odbiornika wideo.

Analizator stanów logicznych

Robiąc cokolwiek przy technice cyfrowej, mikrokontrolerach itp., analizator stanów logicznych może być bardzo przydatny do debugowania. Jest też świetny do rozgryzania gotowych układów 🙂

Od pewnego czasu chodziło mi po głowie, żeby sobie zrobić The Fabulous Logic Analyzer, ale port równoległy, to niestety coś co jest coraz rzadziej spotykane, zwłaszcza w laptopach 🙁

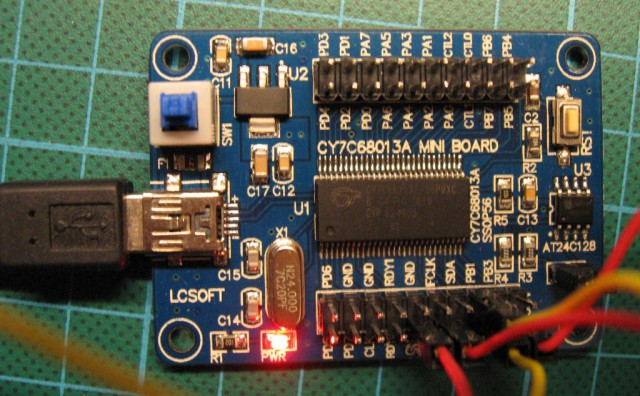

Niedawno widziałem jak działa Saleae Logic16🙂 Robi wrażenie, zwłaszcza, że działa również pod Linuxem. Tylko 100-200 Euro to trochę za dużo za nową zabawkę, więc zacząłem szukać bardziej dostępnych cenowo alternatyw. Po przekopaniu Internetu znalazłem, że starsza wersja Saleae Logic, CWAV USBee SX i inne tańsze analizatory oparte są na tym samym układzie Cypressa: CY7C68013A – i co ciekawe prawie bez dodatkowych części. Wiedząc czego szukać znalazłem na Ebay-u płytkę prototypową Lcsoft CY7C68013A Mini Board za mniej niż $12, którą oczywiście szybko kupiłem 🙂

Nie jest ona kompatybilna z Saleae mimo zaprogramowanego takiego samego identyfikatora USB (VID/PID), ale ponieważ staram się używać otwartego softu o ile się da, to wybrałem Sigrok-a, który to założenie spełnia i radzi sobie z tą płytką.

Po pewnych trudnościach ze spełnieniem zależności (Python3, sdcc i trochę innego dziwnego softu), w końcu się skompilował i zaczął działać. Sigrok na szczęście przychodzi ze swoim firmware do układów Cypressa, więc nic tym razem nie trzeba piratować 🙂

Jest nawet lepiej, płytka Lcsoftu ma zworkę, gdzie można zmienić tryb pracy pomiędzy 'Saleae’ i 'Płytka prototypowa Cypress’.

W trybiie Saleae, Sigrok wrzuca kompatybilny firmware, więc dostępne jest tylko 8 bitów przy samplowaniu 24MHz.

Natomiast po przełączeniu w tryb natywny dostajemy analizator z 16 wejściami. Niestety, dla 16 bitów 24MHz jest już nieosiągalne (max 12MHz), ale można zmniejszyć liczbę próbkowanych wejść i jak zejdziemy do 8 bitów i mniej, to wtedy jest dostępna jest pełna prędkość.

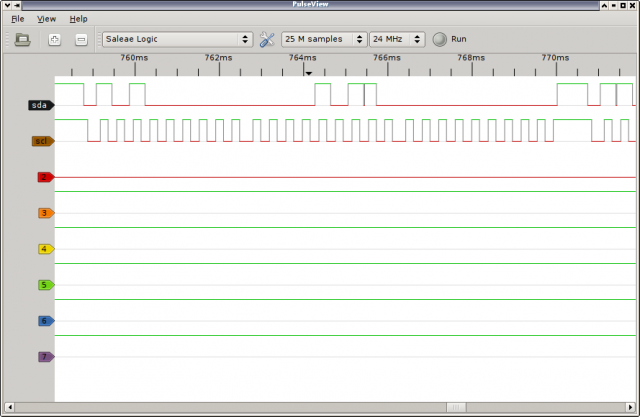

Sogrok jest w miarę nowym projektem, więc gui nie jest niestety jego mocną stroną, ale przynajmniej można posamplować i podejrzeć przebiegi. I to wszystko – nawet zapisu nie da się zrobić 🙁

Za to uruchamiany z linii komend sigrok_cli jest już całkiem potężnym narzędziem.

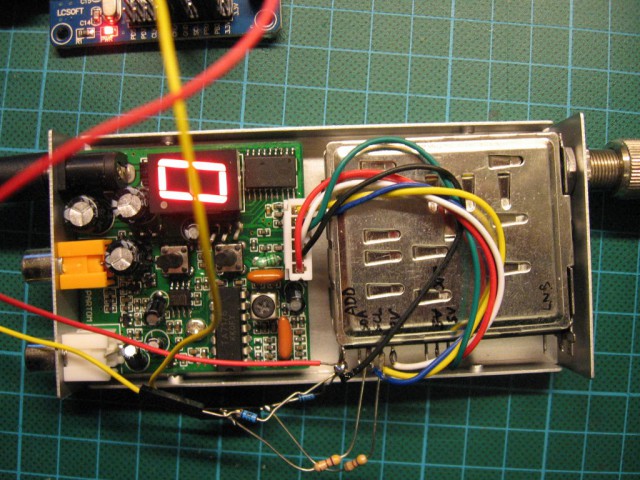

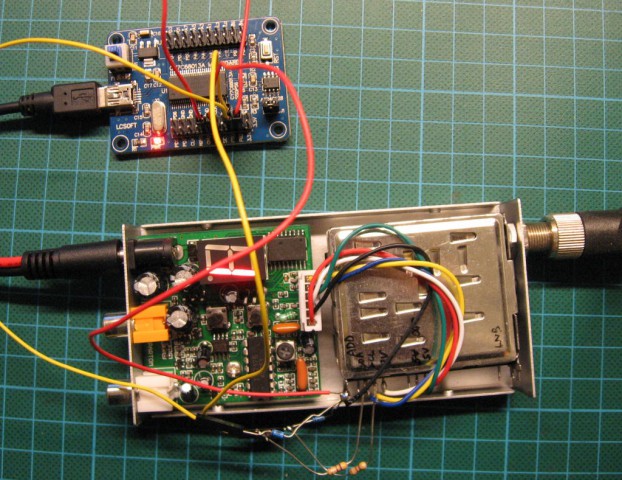

Analizowanie odbiornika wideo

Nadszedł czas coś poanalizować i odbiornik wideo z zestawu Fox700 jest idealny do tego 🙂

Zastanawiałem się od jakiegoś czasu co dokładnie biega w nim na szynie i2c, czyli jak dokładnie programowany jest tuner dla konkretnej częstotliwośći odbioru, i okazja się w końcu znalazła 🙂

Jak widać na zjęciach powyżej, dodałem prosty konwerter poziomów na opornikach i diodach Zenera. Było to konieczne ponieważ odbiornik wideo działa na 5V, a układ Cypressa na 3.3V. Oczywiście na początku próbowałem bez diod Zenera, ale to niestety nie jest AVR i dziwne rzeczy się działy :–)

Samplowanie przy pomocy sigrok_cli:

libsigrok 0.2.0

Acquisition with 8/16 probes at 24 MHz

0:00000000 00000000 00000000 00000000

1:00000000 00000000 00000000 00000000

2:00000000 00000000 00000000 00000000

3:11111111 11111111 11111111 11111111

4:11111111 11111111 11111111 11111111

5:11111111 11111111 11111111 11111111

6:11111111 11111111 11111111 11111111

7:11111111 11111111 11111111 11111111

Jedynki i zera są całkiem fajne, ale prawdziwa siła Sigroka tkwi z możliwości dekodowania protokołów:

$ sigrok-cli -i test.sr -a i2c:sda=0:scl=1

i2c: "START"

i2c: "ADDRESS WRITE" "0x68"

i2c: "ACK"

i2c: "DATA WRITE" "0x05"

i2c: "NACK"

i2c: "STOP"

i2c: "START"

i2c: "ADDRESS READ" "0x50"

i2c: "ACK"

i2c: "DATA READ" "0x00"

i2c: "NACK"

i2c: "STOP"

i2c: "START"

i2c: "ADDRESS WRITE" "0x61"

i2c: "ACK"

i2c: "DATA WRITE" "0x2b"

i2c: "ACK"

i2c: "DATA WRITE" "0x6c"

i2c: "ACK"

i2c: "DATA WRITE" "0x8e"

i2c: "ACK"

i2c: "DATA WRITE" "0xf0"

i2c: "ACK"

i2c: "STOP"

Zapisy na początku, to jakieś śmieci, myślę, że układ sterujący był zaprojektowany do innego układu z dodatkowymi peryferiami, ale w zasadzie to co jest interesujące, to zapisy pod adres 0x61.

Zgodnie z dokumentacją układu SP5055 (synteza używana w większości takich tunerów), adres 0x61 jest adresem pod którym układ zawsze odpowiada, niezależnie od ustawienia stanu na nóżce adresu.

W czasie zapisu zostają przesłane 4 bajty: 2 bajty dzielnika (różne dla każdego kanału) oraz 2 bajty innych ustawień (stan, zewnętrzne wyjścia) – zawsze takie same.

Sprawdźmy więc jaka częstotliwość powinna być zaprogramowana.

Dzielnik w powyższym przykładzie wynosi 0x2b6c (MSB jest transmitowane najpierw) = 11116

Zgodnie ze specyfikacją układu, częstotliwość dostrojenia wynosi:

f = dzielnik * 16 * Fcomp

Fcomp jest częstotliwością z podłączonego kwarcu lub zewnętrznego generatora (typowo 4MHz) podzieloną przez 512, więc:

f = dzielnik * 16 * 4000000 / 512

W tym przypadku synteza/generator jest natrojony na 1389500000Hz = 1389.5MHz

Ale to nie koniec – trzeba jeszcze odjąć częstotliwość pośrednią, czyli w tym tunerze 479.5MHz.

Czyli w rzeczywistości tuner jest dostrojony do częstotliwości 910MHz co odpowiada dokładnie kanałowi 0, który był ustationy w odbiorniku w czasie testu.

Sukces! 🙂

Jedną z rzeczy, które mi brakuje w sigrok_cli jest brak timestampów (chociaż opcją -v można zobaczyć liczbę sampli), ale ponieważ jest to otwarty soft, to może ktoś to prędzej czy później dopisze (może nawej ja) 😉

Na dzisiaj już wiem jak programować tuner, więc mogę zrobić swój kontroler.

Dlaczego? Bo wg. dokumentacji SP5055 niektóre tunery powinny mieć możliwość odczytu z wewnętrznego przetwornika ADC połączonego zazwyczaj z układem demodulatora, co daje informację o dostrojeniu/odstrojeniu między ustawioną częstotliwością, a rzeczywiście odbieraną. Dzięki temu można się dokładniej automatycznie dostroić do nadajnika, który stabilnością niestety nie grzeszy. Dodatkowo istnieje możliwość dostrojenia do dowolnej częstotliwości z zakresie pracy głowicy z rozdzielczością 125kHz 🙂

Dostrajanie z tymi informacjami wielu tunerów jednocześnie też nie jest problemem, więc również zrobienie diversity będzie prostsze 🙂

Hi! Would you mind to give me an email where I could write? Thanks

many thanks, this info was exactly what I was looking for!

question: where did you get the 479.5MHz value, and how did you know that you needed to subtract it from the calculated frequency value? I searched the SP5055 datasheet for this information yet couldn’t find it.

These receivers use old analog satellite tuners in which 479.5MHz is common intermediate frequency. For example you could check datasheet of this one: http://www.dpcav.com/xcart/Comtech-BSS479LAIDF-Analog-Tuner-Module.html

So, having intermediate frequency you have only two choices: pll should make lower or higher frequency with offset of 479.5MHz to received frequency. Typically higher one is choosen. In these tuners is reasonable as it’s lower receiving frequency is about 900MHz (960-480=trouble).

hi and thanks

i want to used tuner with avr. but I do not know how and what kind of tuner should I use? (i2c)

I think the tuner ” sharp BSFJ78G29 ” is good because pll- i2c type, but I do not know how to set : the frequency, symbol rate, vertical or horizontal,…?

can you help me? something like notes about BSFJ78G29 i2c protocol and …..

thanks alot

It looks like this tuner have SP5655 tuner which is almost the same as SP5055. If you google for 'sharp BSFJ78G29′, you can find tuner datasheet. It clearly states that pll chip is SP5655 which is the one you should talk to via i2c. Datasheet for SP5655 is also easily found by google.

Do you found some stock of this tuners? Narrow bandwidth is quite good feature. Maybe I could buy one or more if price is good 🙂

About symbol rate and polarization – what do you want to do with it? It’s analog tuner and I think that almost nothing is available these days on satellite in that way. Symbol rate is domain of digital transmission. Polarisation is also another story as it is modulation of power supply for receiving head, and this is also not related with tuner iself.

thanks majek

i want to analysis some sat frequency features for example signal strength,…. but i do not know How to do it? i searched but i founded some thing like sharp tuner. In your opinion, what tuner I choose?(digital and i2c if possible)

Digital tuners differ a lot from analog ones. In analog almost everything important is inside tuner module, everything outside is just audio separation, equalization and control. Digital tuner is another story – much harder for hobbyist. I’m not familiar with all that demodulation, i/q things and so on (which is processed outside of tuner module), so in this part I couldn’t help you.

So, for analog sattelite – it quite easy to use tuner module to do something (it has rssi analog output, information about frequency lock/deviation is availavle from i2c registers).

For digital measurement I would definitely get PC satellite card – there is a lot of tools which shows signal strength, ber, transport streams, etc in real time. From my experience tuning to get maximum gain sometimes doesn’t work – it’s better to do fine tuning based on ber – and to do it you need complete receiver.

thanks alot majek with you help i can set frequency but

How to check signal information for example signal strength with sharp BSFJ78G29 tuner? (true signal or not)

Signal strength should be available on AGC OUT pin – it’s analog value.

Additionally you could check internal ADC on P6 and FL flag to check if frequency is locked right (assuming that this tuner have such internal connection).

For some clues you could check datasheet of other tuner: http://www.dpcav.com/data_sheets/Comtech_BSS-479.pdf

U mnie w tunerze (receiver dla modelarskich nadajników video 1.2G), właściwie głowicy, siedzi nie sp5055 a TA550A (toshiby) z kwarcem 4MHz i TA8804 z kwarcem 479,58 (okrągłe ustrojstwo, może to nawet generator jest).

Miałem kłopot ze znalezieniem datasheetu od tego TA550A – może kolega pomoże.

Dzięki z góry za pomoc.

Nie znalazłem nic do TA550A, ale podejrzewam, że jest kompatybilny z SP5055. Też typowo wymaga kwarcu 4MHz i raczej dziwne byłoby jakby gadał jakimś innym protokołem. Najlepiej wziąć jakiś analizator stanów logicznych i się przekonać 🙂

Co do 'kwarcu’ 479.58, to jest to filtr pośredniej częstotliwości. Od niego zależy selektywność odbiornika i dlatego często jest wymieniany na węższy (do satelity stosuje się szerokie, ale do bezpośredniego odbioru na 1.2G typowy jest za szeroki i łapie też dużo śmieci i sąsiednie kanały).

Hi there,

Great info! 🙂

Did your board come with firmware to use as an analyser, or did your download/write your own?

Hi All, thank you for this info.

Finally I tried also to pilot this RX 23 cm, and it works fine on the I2C address „2C”. with a single PIC 16F84A and a F6ICX program for COMTECH receiver…

Now I 'm rewriting the same prog for arduino nano and I2C LCD…